Parallel Input Serial Output Shift Register Vhdl Code

0426

Answer to Design and implementation of 8 bit serial/ parallel input serial output shift register using behavioral style of modelli. This code is serial input serial output but not sure. Plz check it? Shall you provide or type the code of parallel input serial output?? Library ieee. In VHDL, a for loop executes in zero time. Jul 17, 2013. Parallel Out Shift Register using D-Flip Flop (VHDL Code). Parallel In - Serial OUT Shift Register. Design of Serial In - Parallel Out Shift.

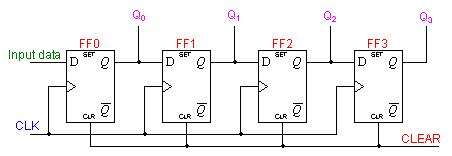

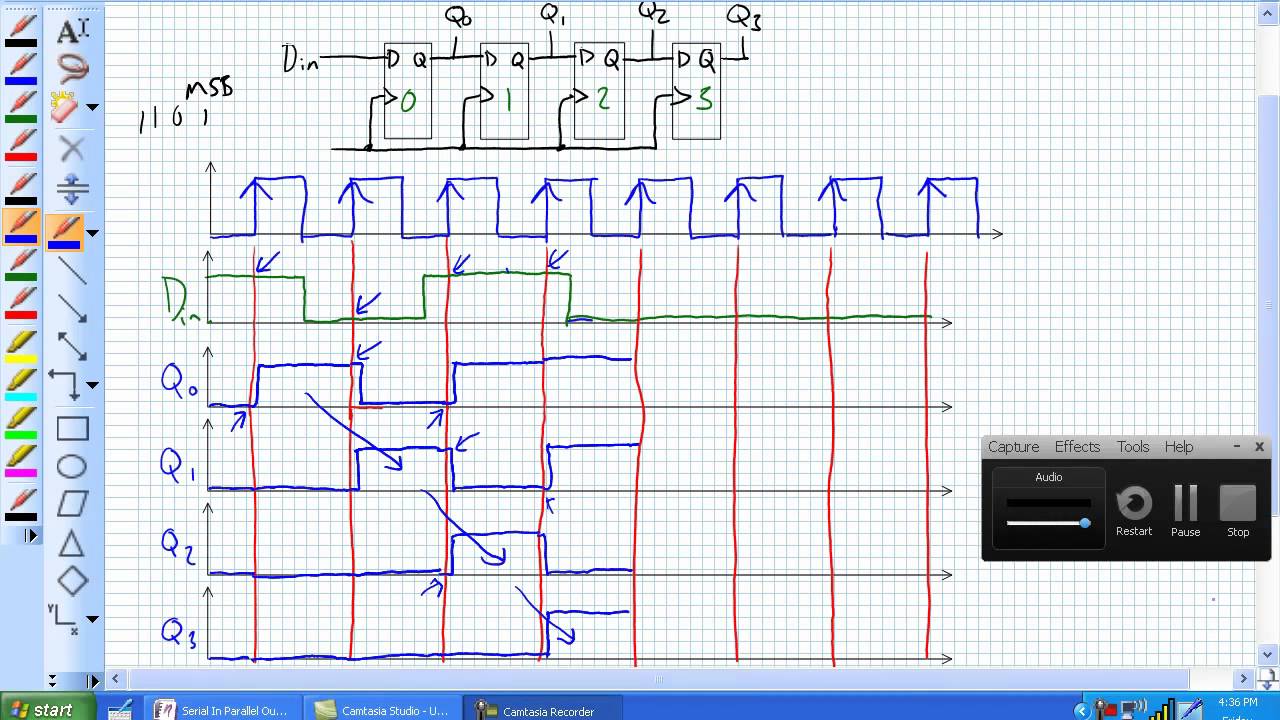

Design of Parallel In - Serial OUT Shift Register using Behavior Modeling Style -| Output Waveform : Parallel IN - Serial OUT Shift Register |

Verilog CODE -

//-----------------------------------------------------------------------------

//

// Title : parallel_in_serial_out

// Design : vhdl_upload2

// Author : Naresh Singh Dobal

// Company : nsdobal@gmail.com

// Verilog HDL Programs & Exercise with Naresh Singh Dobal.

//

//-----------------------------------------------------------------------------

//

// File : Parallel IN - Serial OUT Shift Register.v

module parallel_in_serial_out ( din ,clk ,reset ,load ,dout );

output dout ;

reg dout ;

reg dout ;input [3:0] din ;

wire [3:0] din ;

input clk ;

wire clk ;

input reset ;

wire reset ;

input load ;

wire load ;

reg [3:0]temp;

always @ (posedge (clk)) begin

if (reset)

Serial Input Serial Output Shift Register

temp <= 1;

else if (load)

temp <= din;

else begin

dout <= temp[3];

Parallel Input Serial Output Shift Register Vhdl Code

temp <= {temp[2:0],1'b0};end

end

endmodule